# **PEC - Paraconsistent Electronic Circuits**

### João Inácio da Silva Filho Jair Minoro Abe

Faculdade SENAC de Ciências Exatas e Tecnologia Rua Galvão Bueno, 430 01506-000 São Paulo - SP- Brazil

Institute For Advanced Studies - University of São Paulo Av. Prof. Luciano Gualberto, trav. J, 374, térreo, 05508 - 900 São Paulo - SP - Brazil

#### Abstract

In this work we present digital circuits (logical gates COMPLEMENT, AND, OR) inspired in a class of paraconsistent annotated logics  $P\tau$ . These circuits allow "inconsistent" signals in a nontrivial manner in their structure. Such circuits consist of six states; due the existence of literal operators to each of them, the underlying logic is functionally complete; it is a many-valued and paraconsistent (at least "semantically") logic.

**Key words:** Paraconsistency and implementing electronic circuits, paraconsistent logical gates, paraconsistent electronic circuits.

### **1** Introduction

In this work we present digital circuits (logical gates COMPLEMENT, AND, OR) inspired in a class of paraconsistent annotated logics  $P\tau$  (see [Da Costa, Abe & Subrahmanian 91] and [Abe 92]). These circuits allow "inconsistent" signals in a nontrivial manner in their structure.

Such circuits consist of six states; due the existence of literal operators to each of them, the underlying logic is functionally complete (by a very known result due to [Rosser & Turquette 52]); it is a many-valued and paraconsistent (at least "semantically") logic.

The simulations were made at 50 MHz, 1.2  $\mu$ m, by using the software AIM-SPICE, version 1.5a.

As far as we know, these results seem to be pioneering in using the concept of paraconsistency in the theory of electronic circuits. The applications appear to be large in horizon: it expands the scope of applications where conflicting signals are common,

International Journal of Computing Anticipatory Systems, Volume 9, 2001 Edited by D. M. Dubois, CHAOS, Liège, Belgium, ISSN 1373-5411 ISBN 2-9600262-2-5 such as in sensor circuits in robotics, industry automation circuits, race signal control in electronic circuits, and many other fields.

Let us consider a finite lattice of *truth-values*  $\tau = \langle |\tau|, \leq \rangle$ , where  $|\tau| = \{0, \frac{1}{2}, \frac{1}{4}, \frac{3}{4}, 1, \top\}$ . Intuitively, the elements of  $\tau$  can be read:<sup>1</sup>

$\frac{1}{2} \Rightarrow$  undefined

- $1 \Rightarrow true$

- $0 \Rightarrow false$

$\frac{1}{4} \Rightarrow less false$

$\frac{3}{4} \Rightarrow less true$

$T \Rightarrow inconsistent$

The underlying order is represented as follows

Figure 1 - Lattice SIX

We also define an operator  $\sim: |\tau| \rightarrow |\tau|$  as  $\sim(1) = 0$ ,  $\sim(0) = 1$ ,  $\sim(1/4) = 3/4$ ,  $\sim(3/4) = 1/4$ ,  $\sim(1/2) = 1/2$ ,  $\sim(\top) = \top$ . So, such operator has the "meaning" of negation. The tension levels of the circuit and the logical values are described as follows:

| Proposition   |          |

|---------------|----------|

| Logical value | Tension  |

| 0             | -4 volts |

| 1             | +4 volts |

| Annotat       | tion      |

|---------------|-----------|

| Logical value | Tension   |

| 0             | - 4 volts |

| 1/4           | - 2 volts |

| 1/2           | 0 volts   |

| 3/4           | + 2 volts |

| 1             | + 4 volts |

| Т             | >+4 volts |

Figure 2 – Logical values and tension levels

<sup>&</sup>lt;sup>1</sup> We are aware that the terminology employed is unhappy, but we will keep them throughout in this paper.

## 2 Literal operators

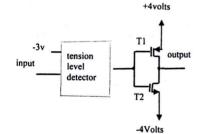

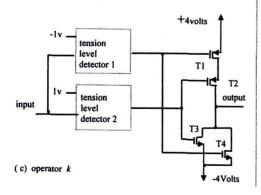

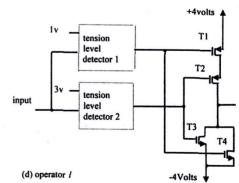

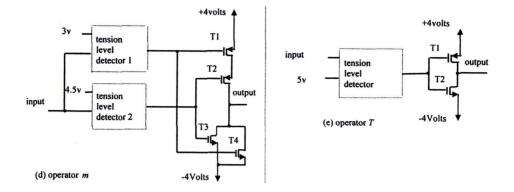

Let us present the logical gates of the literal operators. Firstly, we introduce the literal operators *i*, *j*. *k*, *l*, *m*,  $\top$ .

| Input | Output |

|-------|--------|

| 0     | 1      |

| 1/4   | 0      |

| 1/2   | 0      |

| 3/4   | 0      |

| 1     | 0      |

| Т     | 0      |

| Opera |        |

|-------|--------|

| Input | Output |

| 0     | 0      |

| 1/4   | 1      |

| 1/2   | 0      |

| 3/4   | 0      |

| 1     | 0      |

| Т     | 0      |

| Operator k |        |   |  |

|------------|--------|---|--|

| Input      | Output |   |  |

| 0          | 0      |   |  |

| 1/4        | 0      |   |  |

| 1/2        | 1      | ] |  |

| 3/4        | 0      | 7 |  |

| 1          | 0      |   |  |

| Т          | 0      | 1 |  |

Operator l

Input

Output

0

0

1/4

0

1/2

0

1

0

0

3/4

1

Т

| Input | Output |

|-------|--------|

| 0     | 0      |

| 1/4   | 0      |

| 1/2   | 0      |

| 3/4   | 0      |

| 1     | 1      |

| Т     | 0      |

| Operator n |        |  |

|------------|--------|--|

| Input      | Output |  |

| 0          | 0      |  |

| 1/4        | 0      |  |

| 1/2        | 0      |  |

| 3/4        | 0      |  |

| 1          | 0      |  |

| Т          | 1      |  |

Figure 3 - Truth table and logical gates

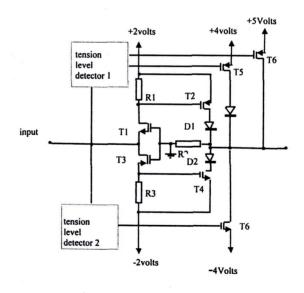

## **3** Logical Gate Complement

| Input | Output |  |  |

|-------|--------|--|--|

| 0     | 1      |  |  |

| 1/4   | 3/4    |  |  |

| 1/2   | 1/2    |  |  |

| 3/4   | 1/4    |  |  |

| 1     | 0      |  |  |

| Т     | Т      |  |  |

Figure 4 – Truth table and circuit of the operator Complement.

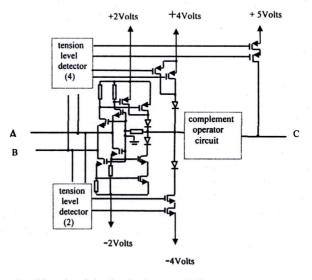

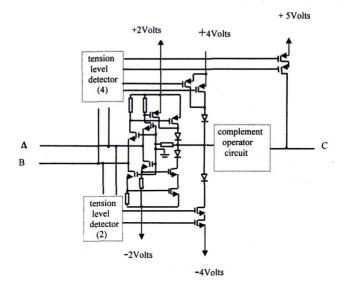

# 4 Logical gates AND and OR

| A   | ND  |     |  |     | OR  |     |

|-----|-----|-----|--|-----|-----|-----|

| A   | В   | C   |  | A   | B   | С   |

| 0   | 0   | 0   |  | 0   | 0   | 0   |

| 0   | 1/4 | 0   |  | 0   | 1/4 | 1/4 |

| 0   | 1/2 | 0   |  | 0   | 1/2 | 1/2 |

| 0   | 3/4 | 0   |  | 0   | 3/4 | 3/4 |

| 0   | 1   | 0   |  | 0   | 1   | 1   |

| 0   | Т   | 0   |  | 0   | Т   | Т   |

| 1/4 | 0   | 0   |  | 1/4 | 0   | 1/4 |

| 1/4 | 1/4 | 1/4 |  | 1/4 | 1/4 | 1/4 |

| 1/4 | 1/2 | 1/4 |  | 1/4 | 1/2 | 1/2 |

| 1/4 | 3/4 | 1/4 |  | 1/4 | 3/4 | 3/4 |

| 1/4 | 1   | 1/4 |  | 1/4 | 1   | 1   |

| %   | Т   | 0   |  | 1/4 | T   | Т   |

| 1/2 | 0   | 1/4 |  | 1/2 | 0   | 1/2 |

| 1/2 | 1/4 | 1/2 |  | 1/2 | 1/4 | 1/2 |

| 1/2 | 1/2 | 1/2 |  | 1/2 | 1/2 | 1/2 |

| 1/2 | 3/4 | 1/2 |  | 1/2 | 3/4 | 3/4 |

| 1/2 | 1   | 1/2 |  | 1/2 | 1   | 1   |

| 1/2 | T   | 0   |  | 1/2 | T   | T   |

| 3/4 | 0   | 1/4 |  | 3/4 | 0   | 3/4 |

| 3/4 | 1/4 | 1/4 |  | 3/4 | 1/4 | 3/4 |

| 3/4 | 1/2 | 1/2 |  | 3/4 | 1/2 | 3/4 |

| 3/4 | 3/4 | 1/4 |  | 3/4 | 3/4 | 3/4 |

| %   | 1   | 3/4 |  | 3/4 | 1   | 1   |

| 3/4 | Т   | %   |  | 3/4 | T   | T   |

| 1   | 0   | 0   |  | 1   | 0   | 1   |

| 1   | 1/4 | 1/4 |  | 1   | 1/4 | 1   |

| 1   | 1/2 | 1/2 |  | 1   | 1/2 | 1   |

| 1   | 3/4 | 3/4 |  | 1   | 3/4 | 1   |

| 1   | 1   | 1   |  | 1   | 1   | 1   |

| 1   | Т   | Т   |  | 1   | Т   | Т   |

| Т   | 0   | 0   |  | T   | 0   | Т   |

| Т   | 1/4 | 1/4 |  | Т   | 1/4 | Т   |

| T   | 1/2 | 1/2 |  | Т   | 1/2 | Т   |

| T   | 3/4 | 1/4 |  | T   | 3/4 | T   |

| T   | 1   | 1   |  | Т   | 1   | T   |

| T   | T   | T   |  | T   | T   | T   |

Figure 5 – Truth table of the logical gates AND and OR

Figure 6 – Circuit of the logical gate AND

Figure 7 – Circuit of the logical gate OR

All the circuits were implemented by using the *CMOS* transistors. As we mentioned above, there exits an underlying logic such that these studies are functionally complete. So, any other circuits build can be expressed by the circuits AND and COMPLEMENT. Moreover, as an application we have considered a Paraconsistent Analyzer Module: it is a circuit that analyses signals detecting conflicting signals, and furnishes an adequate treatment to them. Details are in a forthcoming paper.

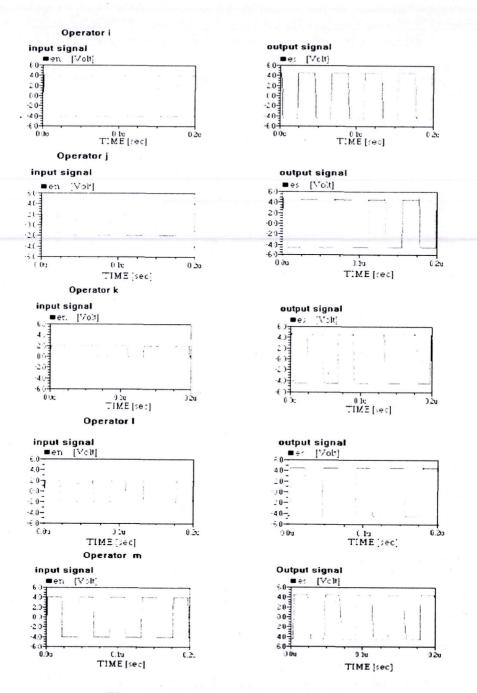

### **5** Simulations

The Figures 8, 9 and 10 bellow show us the simulation results made with the literal operator circuits, complement circuit, logical gates AND and OR, respectively. All circuits were implemented with *CMOS* transistors and simulated with AIMSPICE.

As it can be verified in the Figure 8, where it is presented the literal operators results, the 4 Volts output corresponds to the logical level 1. They are related exactly to the tension levels specified by the table of the Figure 2.

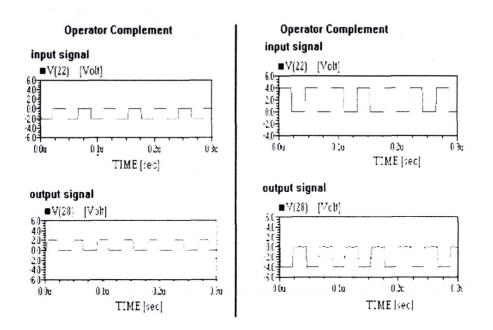

In the Figure 9, concerning complement operator, the output signal is the complemented signal applied in the input.

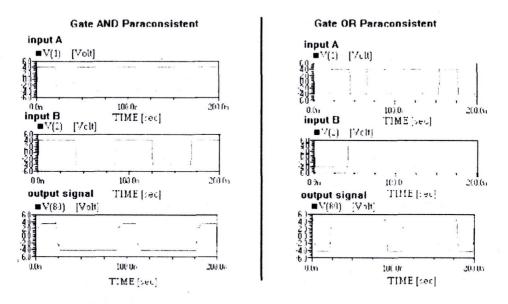

In the Figure 10, simulation of the logical circuits AND and OR, we can see that the results are the maximization and minimization according to the true table of the Figure 5.

Figure 8 – Simulation results of the literal operators

Figure 9 – Simulation results of the complement operator

Figure 10 – Simulation results of the circuit logical gates AND and OR

### **6** Conclusions

We have implemented paraconsistent electronic circuits based on a class of paraconsistent annotated logics. As far as we know these studies are pioneering in the electronic circuit theory. The *PAM* shows the various applications that these circuits can have in several areas where conflicting situations are common: robotics, industry automation circuits, race signal control in electronic circuits, and many other fields, mainly in AI.

The paraconsistent logics give us the logical and philosophical bases to treat the concept of contradiction. This works came to establish that it is possible to materialize that concept physically trough suitable electronic circuits, opening a new branch of researching in this field.

#### References

[Abe 92] ABE, J.M., *Fundamentos da Lógica Anotada* (Foundations of Annotated Logics) (in Portuguese), Ph.D. Thesis, University of São Paulo, São Paulo, 1992.

[Abe 97] ABE, J.M., Some Aspects of Paraconsistent Systems and Applications, *Logique et Analyse*, 157(1997), 83-96.

[Abe & Da Silva Filho 96] ABE, J.M. & J.I. DA SILVA FILHO, Implementação de Circuitos eletrônicos de funções lógicas paraconsistentes Radix N (in Portuguese), *Coleção Documentos, Série Lógica e Teoria da Ciência,* Institute For Advanced Studies, University of São Paulo, nº 22, 37p., 1996.

[Abe & Da Silva Filho 98] ABE, J.M. & J.I. DA SILVA FILHO, Inconsistency and Electronic Circuits, *Proceedings of The International ICSC Symposium on Engineering of Intelligent Systems* (EIS'98), Volume 3, Artificial Intelligence, Editor: E. Alpaydin, ICSC Academic Press International Computer Science Conventions Canada/Switzerland, ISBN 3-906454-12-6, 191-197, 1998.

[Da Costa, Abe & Subrahamanian 91] DA COSTA, N.C.A., J.M. ABE & V.S. SUBRAHMANIAN, Remarks on annotated logic, *Zeitschrift f. math. Logik und Grundlagen d. Math.* 37, pp 561-570, 1991.

[Da Silva Filho 97] DA SILVA FILHO, J.I., "Implementação de circuitos lógicos fundamentados em uma classe de Lógicas Paraconsistentes Anotadas", Dissertação de Mestrado-EPUSP, São Paulo, 1997.

[Da Silva Filho & Abe 97a] DA SILVA FILHO, J.I. & J.M. ABE, Lógica paraconsistente anotada e circuitos de portas lógicas, *Coleção Documentos, Série Lógica e Teoria da Ciência*, IEA-USP,  $n_0$  23, 41p., 1997.

[Reiter 80] REITER, R. "A logic for Default Reasoning", Artificial Intelligence vol.13 pp.81-132, 1980.

[Rine 84] RINE, D.C & Vranesic, Z.G. & Smith, K.C., "Electronic Circuits for Multi-valued digital Systems" *New York:North-Holland*, 1984.

[Rosser & Turquette 52] ROSSER, J.B. & A. TURQUETTE, Many-Valued Logics, North Holland Publishing Company, 1952, (Second Edition, Greenwood).

[Weste & Eshraghian 85] WESTE, N.H.E. & K. ESHRAGHIAN, "Principles of CMOS VLSI Design" *Wesley Ed. Addison Publishing Company*, USA, 1985.